在高速数字电路设计中,信号完整性(SI)问题已成为制约系统性能的关键瓶颈。时钟频率的提升与信号边沿的变陡,使得传输线效应日益显著。若缺乏有效的 SI 分析,产品极易出现误码、死机或启动失败。本文将解析信号完整性分析的核心流程与方法,助力工程师优化设计。

一、前期仿真建模

SI 分析应始于设计阶段,通过仿真预测潜在风险。

- 模型提取:获取 IBIS 模型或 S 参数模型,准确描述驱动器、接收器及互联通道的电气特性。

- 拓扑结构分析:检查走线长度、分支结构及端接方式,评估反射风险。

- 时序仿真:建立 Setup/Hold 时间预算,确保数据在时钟沿有效窗口内稳定。

仿真可提前发现阻抗不连续、端接匹配不当等问题,降低后期改版成本。

二、关键测试指标与方法

实物测试是验证仿真结果及诊断问题的必要手段。

| 测试指标 | 测试仪器 | 关注重点 |

|---|---|---|

| 眼图测试 | 高带宽示波器 | 眼高、眼宽、抖动幅度 |

| TDR 阻抗测试 | 时域反射计 | 阻抗连续性、过孔阻抗突变 |

| 串扰测试 | 网络分析仪/示波器 | 近端串扰、远端串扰幅度 |

眼图是评估信号质量最直观的工具,眼图闭合程度直接反映误码率风险。

三、反射与端接优化

阻抗不匹配导致的反射是 SI 问题的常见根源。

- 源端端接:在驱动器输出端串联电阻,匹配传输线阻抗,吸收反射波。

- 终端端接:在接收端并联电阻至地或电源,消除负载端反射。

- 走线控制:避免直角走线,减少过孔数量,保持参考平面完整。

通过 TDR 测试定位阻抗突变点,针对性调整线宽或层叠结构。

四、电源完整性协同分析

信号完整性与电源完整性(PI)密不可分。

- 同步开关噪声(SSN):多信号同时翻转导致电源地弹,影响信号电平。

- 去耦电容优化:合理布局电容,降低电源平面阻抗,提供瞬时电流。

需联合仿真 SI 与 PI,确保供电网络在高频下仍保持稳定。

总结:信号完整性分析需结合仿真与测试,贯穿产品设计全生命周期。重点关注阻抗控制、端接匹配及电源噪声抑制。通过系统化的 SI 分析,可显著提升高速电路的信号质量,降低误码率,确保系统长期稳定运行。

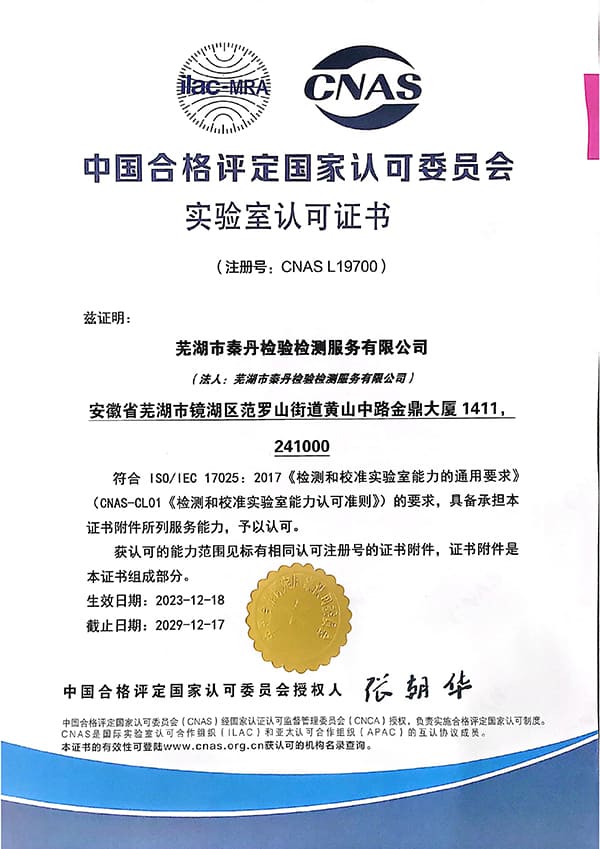

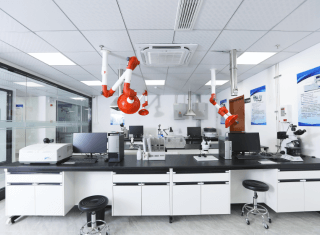

汇策晟安检测提供专业的信号完整性分析与测试服务。我们配备高速示波器、矢量网络分析仪及仿真软件,可协助客户进行 PCB 前仿真评审、阻抗测试及眼图验证。团队拥有丰富的硬件调试经验,能够精准定位信号失真根因,提供有效的整改方案,提升产品设计成功率。

alt="微信二维码">

alt="微信二维码">